## (19)日本国特許庁 (JP)

## (12) 公開特許公報(A)

(11)特許出願公開番号

# 特開平5-233517

(43)公開日 平成5年(1993)9月10日

(51)Int.Cl.<sup>5</sup>

識別記号 月

庁内整理番号

FΙ

技術表示箇所

G 0 6 F 13/12

3 4 0 C 7230-5B

審査請求 未請求 請求項の数2(全 5 頁)

(21)出願番号

特願平4-69681

(22)出願日

平成 4年(1992) 2月19日

(71)出願人 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(72)発明者 稲田 久

東京都港区芝五丁目7番1号 日本電気株

式会社内

(74)代理人 弁理士 高橋 勇

## (54)【発明の名称】 中央制御補助プロセッサ装置

#### (57)【要約】

【目的】 複数の入出力装置からの過度の制御処理要求 に対しても、これに有効に対応し得る中央制御補助プロセッサ装置を提供すること。

【構成】 複数の入出力装置31~に接続され、該複数の入出力装置31~を中央制御装置20に代わって直接制御するプロセッサ回路1と、中央制御装置20に接続され当該中央制御装置20に対し所定の情報交換を行う制御バスインターフェイ回路6とを備えている。そして、中央制御装置20が、必要に応じて複数の入出力装置31~を直接制御するのを許容する制御バス中継回路2を制御バスインターフェイ回路6に併設したこと。

#### 【特許請求の範囲】

【請求項1】 複数の入出力装置に接続され、該複数の入出力装置を中央制御装置に代わって直接制御するプロセッサ回路と、中央制御装置に接続され当該中央制御装置に対し所定の情報交換を行う制御バスインターフェイ回路とを備えた中央制御補助プロセッサ装置において、前記中央制御装置が必要に応じて前記複数の入出力装置を直接制御するのを許容する制御バス中継回路を前記制御バスインターフェイ回路に併設したことを特徴とする中央制御補助プロセッサ装置。

【請求項2】 複数の入出力装置に接続され、該複数の入出力装置を中央制御装置に代わって直接制御するプロセッサ回路と、中央制御装置に接続され当該中央制御装置に対し所定の情報交換を行う制御バスインターフェイ回路とを備えた中央制御補助プロセッサ装置において、前記中央制御装置が必要に応じて前記複数の入出力装置を直接制御するのを許容する制御バス中継回路を前記制御バスインターフェイ回路に併設すると共に、前記複数の入出力装置に対する直接制御の競合を回避せしめる制御バス競合調停回路を前記制御バス中継回路に併設したことを特徴とする中央制御補助プロセッサ装置。

#### 【発明の詳細な説明】

#### [0001]

【産業上の利用分野】本発明は、中央制御補助プロセッサ装置に係り、とくに多数の入出力装置を制御するための中央制御装置の機能を補助するための中央制御補助プロセッサ装置に関する。

#### [0002]

【従来の技術】従来の中央制御補助プロセッサ装置は、中央制御装置の一部の処理を分担するためのプロセッサ機能と、第一の制御バスを介して該中央制御装置と情報交換が可能なプロセッサ間通信機能とを有する。このような構成にあって、多数の入出力装置を用いて実現される一つもしくは複数のサービス機能の実行処理は、階層化されて大きく二分される。

【0003】二分された上位階層は、該中央制御装置によって実行され、二分されたもう一方の下位階層は本中央制御補助プロセッサ装置によって実行される。二分化された処理は中央制御装置と中央制御補助プロセッサ装置とのプロセッサ間通信機能によって、そのインタフェースが保たれる。第二の制御バスに接続される多数の入出力装置の直接制御は中央制御補助プロセッサ装置によって実施されるようになっている。

#### [0004]

【発明が解決しようとする課題】この従来の中央制御補助プロセッサ装置では、中央制御装置が第二制御バスに収容される入出力装置の制御を直接実行する手段を有していない。このため、サービス機能の実行処理が階層化され得るものには問題が無いが、処理が階層化できないサービス機能については、入出力装置の制御が実行でき

ないという問題があった。また、この問題を解決するために入出力装置の制御処理のみを中央制御補助プロセッサ装置に分離する方法もあるが、中央制御装置が直接入出力装置を制御する場合に比べて処理時間が増大し、処理能力を低下させてしまうという不都合が生じていた。 【0005】

【発明の目的】本発明は、かかる従来例の有する不都合を改善し、とくに、複数の入出力装置からの過度の制御処理要求に対しても、これに有効に対応し得る中央制御補助プロセッサ装置を提供することを、その目的とする。

#### [0006]

【課題を解決するための手段】本発明では、複数の入出力装置に接続され、該複数の入出力装置を中央制御装置に代わって直接制御するプロセッサ回路と、中央制御装置に接続され当該中央制御装置に対し所定の情報交換を行う制御バスインターフェイ回路とを備えた中央制御補助プロセッサ装置において、中央制御装置が必要に応じて複数の入出力装置を直接制御するのを許容する制御バス中継回路を制御バスインターフェイ回路に併設する等の構成を採っている。これによって前述した目的を達成しようとするものである。

#### [0007]

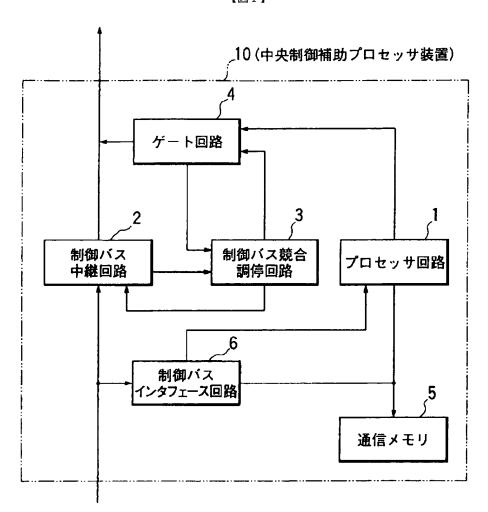

【実施例】以下、本発明の一実施例を図1ないし図2に基づいて説明する。この図1ないし図2に示す実施例は、複数の入出力装置に接続され、該複数の入出力装置を中央制御装置に代わって直接制御するプロセッサ回路1と、中央制御装置に接続され当該中央制御装置に対し所定の情報交換を行う制御バスインターフェイ回路6とを備えている。さらに、この図1に示す実施例においては、中央制御装置が必要に応じて複数の入出力装置を直接制御するのを許容する制御バス中継回路2を制御バスインターフェイ回路6に併設すると共に、複数の入出力装置に対する直接制御の競合を回避せしめる制御バス競合調停回路3が制御バス中継回路6に併設されている。

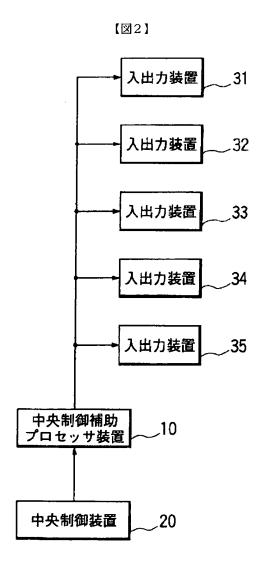

【0008】これを更に詳述すると、中央制御装置20は、第一の制御バスによって中央制御補助プロセッサ装置10に接続され、中央制御補助プロセッサ10を介して入出力装置31~35の制御を行う。中央制御補助プロセッサ10と入出力装置31~35間は、第二の制御バスによって接続されている(図2参照)。

【0009】図1は本発明の一実施例の中央制御補助プロセッサ装置10のブロック図である。第一の制御バスは、制御バス中継回路2によって第二の制御バスへ接続されている。中央制御装置の一部処理を分担,実行するプロセッサ回路1は、制御バスインタフェース回路6と第一の制御バスを介して中央制御装置20と接続されるとともに、中央制御装置20との通信を実現する通信メモリ5と接続される。一方、プロセッサ回路1は、ゲート回路4を介して第二の制御バスへ接続され、プロセッ

サ回路1による入出力装置31~35の制御を可能とする。制御バス競合調停回路3は、制御バス中継回路2とゲート回路4に接続され、中央制御装置20又は中央制御補助プロセッサ装置10による入出力装置31~35の制御実行時、第二の制御バスの使用をそれぞれに許可する。

,1

【0010】実行処理が階層化され中央制御装置20と中央制御補助プロセッサ装置10が処理を分担する場合は、制御バスやインタフェース回路6と通信メモリ5を介して中央制御装置20と中央制御補助プロセッサ装置10とが通信を行う。この場合、入出力装置31~35の制御は中央制御補助プロセッサ装置10が受け持ち、ゲート回路4と第二の制御バスを介してプロセッサ回路1が実行する。この場合もゲート回路4は、制御バス競合調停回路3へ第二の制御バスの使用権を要求し、その許可を受ける。

【0011】一方、実行処理が階層化できないものは中央制御装置20だけで処理され、中央制御補助プロセッサ装置10はバス中継回路として機能する。すなわち、中央制御装置20は、制御バス中継回路2を介して直接第二の制御バス上の入出力装置31~35の制御を行う。この場合、制御バス中継回路2は制御バス競合調停回路3へ第二の制御バスの使用権を要求し、その許可を受ける。通常、前記の動作は時間的に同時進行するが、第二の制御バスは制御バス競合調停回路3によって中央

制御装置20とプロセッサ回路1によって時分割に使用 されることになる。

#### [0012]

【発明の効果】以上説明したように、本発明によると、実行処理が階層化され、中央制御装置と中央制御補助プロセッサ装置に処理分散が可能なサービスについてはもちろん、実行処理が階層化できないサービスについても中央制御装置単独での処理が可能と成るという従来にない優れた中央制御補助プロセッサ装置を提供することができる。

#### 【図面の簡単な説明】

【図1】本発明の一実施例のブロック図である。

【図2】図1に示した中央制御補助プロセッサ装置を用いたシステムの構成図である。

### 【符号の説明】

- 1 プロセッサ回路

- 2 制御バス中継回路

- 3 制御バス競合調停回路

- 4 ゲート回路

- 5 通信メモリ

- 6 制御バスインタフェース回路

- 10 中央制御補助プロセッサ装置

- 20 中央制御装置

- 31~35 入出力装置

【図1】